Introduction

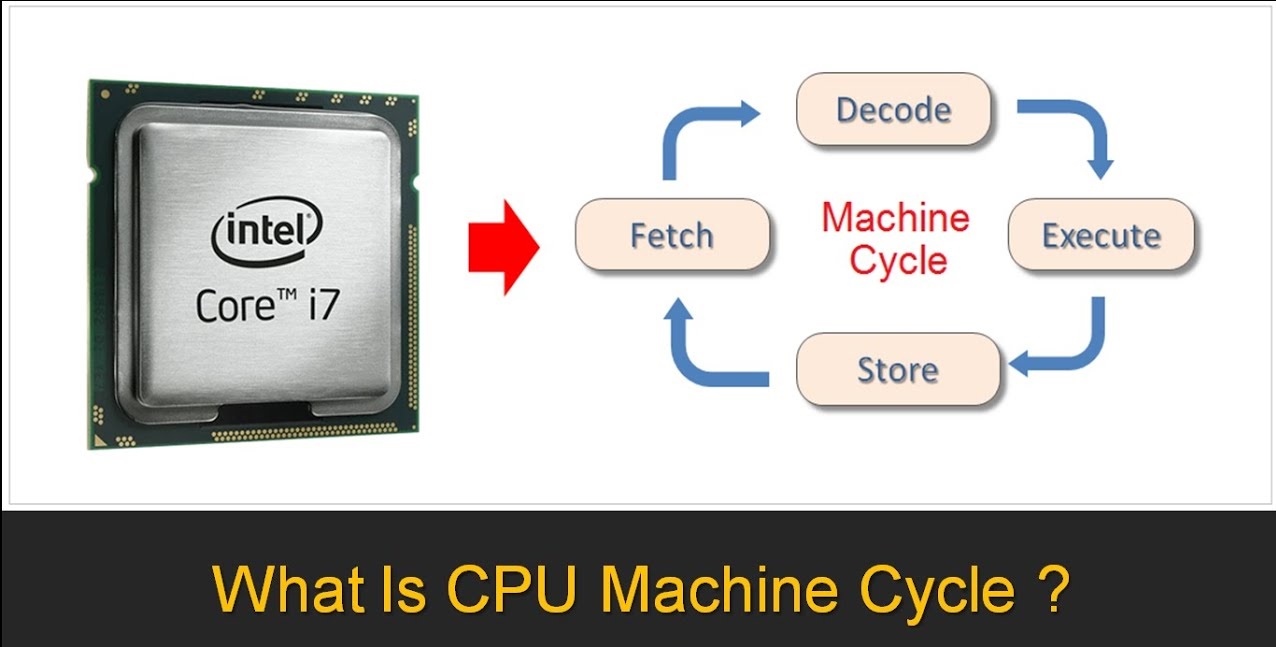

When it comes to understanding the inner workings of a computer, one of the fundamental concepts to grasp is the machine cycle. The machine cycle is the series of events that occur within the central processing unit (CPU) when it carries out the instructions given to it by a program. These instructions are represented as binary code and are processed in a specific order to perform tasks and operations.

During each machine cycle, the CPU goes through several stages to execute the instructions. These stages include fetching the instruction from memory, decoding the instruction to determine what operation to perform, executing the operation itself, and finally storing the results. Each stage is crucial and contributes to the overall functionality of the CPU.

Understanding the machine cycle is essential because it allows us to comprehend how the CPU processes instructions and performs calculations at a lightning-fast speed. It enables us to optimize program execution, identify potential bottlenecks, and improve overall system performance.

In this article, we will delve into the details of each stage of the machine cycle, examining how the CPU actually performs the work described in the commands. We will also explore the factors that can influence the timing of CPU work.

So, without further ado, let’s dive into the fascinating world of the CPU’s machine cycle and explore the intricate processes that power our computers and devices.

What is a Machine Cycle?

A machine cycle, also known as an instruction cycle or processor cycle, is a series of steps that the CPU goes through to execute a single instruction. It is the basic unit of operation for the CPU and is repeated countless times per second to process instructions and perform calculations.

The machine cycle consists of four main stages: fetching, decoding, executing, and storing. Let’s take a closer look at each of these stages:

1. Fetching: During this stage, the CPU retrieves the next instruction from memory. The program counter, a small register within the CPU, holds the address of the next instruction to be executed. The CPU sends a request to the memory controller to fetch the instruction from that address. The fetched instruction is then stored in a special register called the instruction register.

2. Decoding: In this stage, the fetched instruction is deciphered to determine what operation needs to be performed. The instruction is typically encoded in binary format, and the CPU’s control unit interprets the binary codes and translates them into signals that the CPU can understand. The decoding process involves identifying the opcode, which specifies the operation, and any operands that are required for that operation.

3. Executing: Once the instruction has been decoded, the CPU carries out the operation specified by the opcode. This may involve performing mathematical calculations, moving data between registers, accessing or modifying memory locations, or interacting with input/output devices. The exact actions taken by the CPU during the execution stage depend on the specific instruction being executed.

4. Storing: The final stage of the machine cycle is storing the results of the executed instruction. If the instruction involves a calculation or manipulation of data, the outcome is stored back into a register or memory location for future use. Additionally, the program counter is updated to point to the next instruction in memory so that the cycle can repeat with the next instruction.

The machine cycle is a continuous loop that repeats over and over again, allowing the CPU to execute instructions in a sequential manner. By understanding the different stages of the machine cycle, we can gain insight into how the CPU processes instructions and performs complex tasks.

Fetching the Instruction

The first stage of the machine cycle is fetching the instruction from memory. The CPU needs to know which instruction to execute, so it retrieves it from the memory location specified by the program counter.

The program counter (PC) is a register that holds the address of the next instruction to be fetched and executed. It is incremented after each instruction is fetched, ensuring that the CPU moves on to the next instruction in sequence.

To fetch the instruction, the CPU sends a request to the memory controller, specifying the address stored in the program counter. The memory controller responds by retrieving the instruction from the memory address and sending it back to the CPU.

Once the instruction is fetched, it is stored in a special register called the instruction register (IR). The instruction register holds the binary representation of the instruction, allowing the CPU to process it.

Fetching the instruction is a crucial step in the machine cycle, as it determines which operation the CPU will perform. The instruction itself contains the opcode, which specifies the type of operation, and any operands or addressing modes that are required.

In modern CPUs, fetching multiple instructions ahead of time is a common technique known as instruction prefetching. This helps improve performance by reducing the time wasted waiting for instructions to be fetched. By fetching instructions in advance, the CPU can ensure a steady supply of instructions to be executed.

In some cases, fetching the instruction may incur a delay, especially if the CPU needs to wait for the memory controller to retrieve the instruction from main memory. This delay, known as a memory access latency, can impact overall performance and response time.

Overall, fetching the instruction is a critical stage in the machine cycle, as it provides the CPU with the necessary information to execute specific operations. By efficiently retrieving instructions and minimizing delays, the CPU can ensure smooth and efficient execution of instructions.

Decoding the Instruction

Once the instruction has been fetched in the previous stage of the machine cycle, the CPU proceeds to the next step: decoding. In this stage, the CPU interprets the fetched instruction to determine what operation needs to be performed.

During the decoding process, the CPU’s control unit analyzes the binary representation of the instruction stored in the instruction register (IR). The control unit extracts the opcode, which specifies the type of operation, and interprets any additional information such as operands or addressing modes.

The opcode is a binary code that corresponds to a specific instruction or operation. It serves as a command to the CPU, indicating what needs to be done. Common opcodes include arithmetic operations (add, subtract, multiply), logical operations (AND, OR, XOR), and control flow instructions (jump, branch).

In addition to the opcode, the instruction may also contain operands. Operands are the data or addresses on which the instruction operates. They can be immediate values (constants), register contents, memory locations, or combinations of these.

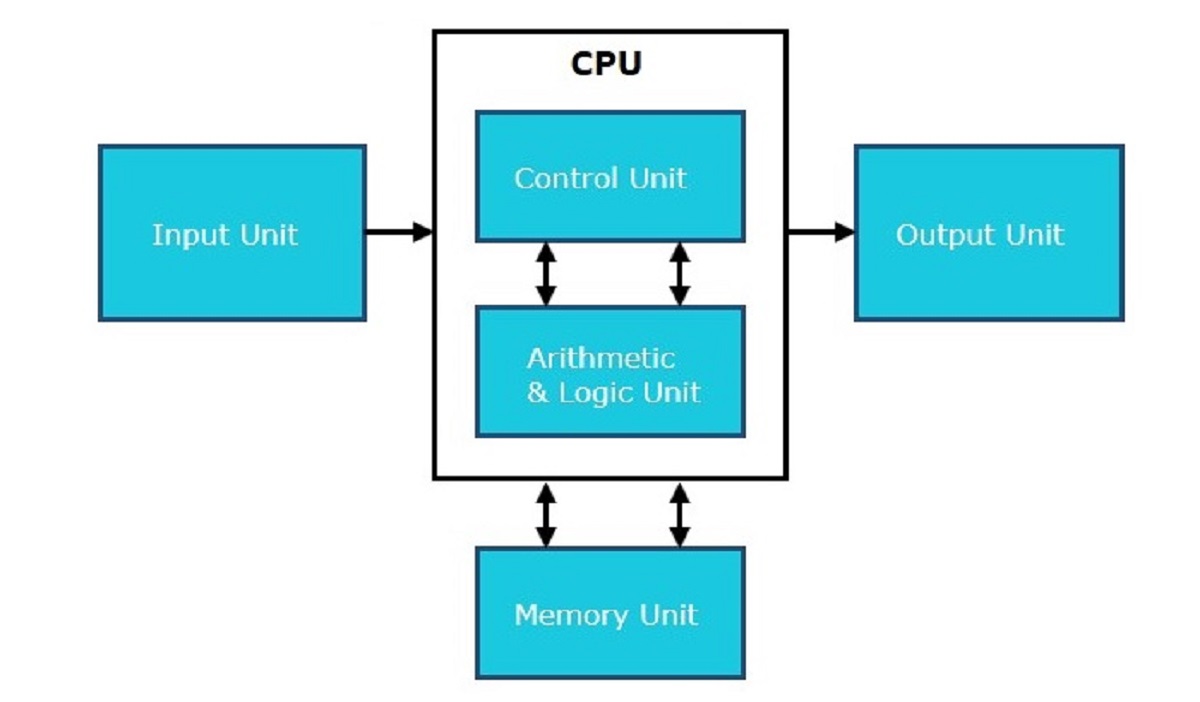

During decoding, the control unit determines the specific operation to be performed based on the opcode and operands. It configures the CPU’s various units, such as the arithmetic logic unit (ALU), to carry out the desired operation.

Decoding is a critical step in the machine cycle, as it ensures that the CPU understands and executes the correct operation. The control unit acts as the “brain” of the CPU, coordinating and directing the various components to execute instructions accurately.

Decoding can be a complex process, especially in CPUs with a wide range of instructions and addressing modes. The control unit must be able to interpret a variety of opcode formats and handle different types of operands. Additionally, modern CPUs often employ microcode, which translates complex instructions into simpler micro-operations for execution.

Efficient decoding is crucial for overall CPU performance. Inadequate decoding can lead to misinterpretation of instructions, resulting in errors or incorrect behavior. On the other hand, well-designed decoding mechanisms can improve instruction execution efficiency and enable the CPU to handle a wide range of tasks effectively.

In modern CPUs, decoding often happens in parallel with other stages of the machine cycle. This allows for faster instruction processing and execution, contributing to the overall speed and performance of the CPU.

Overall, decoding the instruction is a crucial step in the machine cycle, as it enables the CPU to understand and execute the desired operation. By accurately interpreting the opcode and operands, the CPU can prepare itself for the next stage of the cycle: executing the instruction.

Executing the Instruction

After the instruction has been fetched and decoded in the previous stages of the machine cycle, the CPU moves on to the next step: executing the instruction. This stage involves carrying out the specific operation specified by the opcode and operands of the instruction.

During the execution stage, the CPU’s control unit coordinates with other components, such as the arithmetic logic unit (ALU) and registers, to perform the necessary calculations and manipulations. The ALU is responsible for executing arithmetic and logical operations, while the registers store temporary data and results.

The exact actions taken by the CPU during the execution stage depend on the specific instruction being executed. For example, if the instruction is an arithmetic operation like addition, the CPU fetches the operands from registers or memory, performs the calculation using the ALU, and stores the result back into a register or memory location.

Similarly, for instructions involving logical operations or data manipulation, the CPU follows a set of predefined steps to execute the operation. This may involve comparing values, shifting bits, performing bitwise operations, or modifying data in memory or registers.

During the execution stage, the CPU may also interact with other components, such as input/output devices or memory. For example, if the instruction involves reading data from a keyboard or writing data to a disk drive, the CPU coordinates the necessary data transfers between the devices and the memory or registers.

Efficient execution is crucial for overall CPU performance. Factors such as the design of the ALU, the speed of the registers, and the effectiveness of the data transfer mechanisms can significantly impact the execution time of instructions. Optimizations such as pipelining and parallel processing techniques aim to improve the CPU’s execution capabilities and maximize throughput.

In modern CPUs, sophisticated techniques like branch prediction and speculative execution are employed to minimize the impact of conditional instructions and branches on performance. By predicting the outcome of branching instructions, the CPU can speculatively execute subsequent instructions, reducing the potential slowdown caused by conditional jumps.

Overall, the execution stage of the machine cycle plays a vital role in processing instructions and performing computations. By efficiently coordinating the CPU’s various components and following the instruction’s opcode and operands, the CPU can execute the desired operation and move closer to completing the machine cycle.

Storing the Results

Once the instruction has been fetched, decoded, and executed, the CPU moves on to the final stage of the machine cycle: storing the results. This stage involves saving the outcome of the executed instruction to the appropriate location, such as a register or memory.

During the execution stage, the CPU produces a result or modifies data based on the operation specified by the instruction. It is important to store these results back into memory or registers for future use or to update the state of the system.

If the instruction involves a calculation or manipulation of data, the result is typically stored back into a register. Registers are small, high-speed memory locations within the CPU that can be accessed quickly. They are used to hold temporary data and intermediate results during the execution of instructions.

In cases where the instruction modifies data in memory, the CPU writes the updated data back to the corresponding memory location. Storage locations in memory can be addressed directly or indirectly through registers or pointers.

During the storing stage, the CPU updates the necessary registers, memory locations, or other data structures to reflect the changes made by the executed instruction. This ensures that subsequent instructions or operations can access the correct data and continue the program’s execution.

Efficient storage of results is crucial for proper program execution and system operation. Incorrect storage or failure to update the necessary data structures can lead to errors, data corruption, or unexpected behavior in the program.

In addition to storing the results, the program counter (PC) is updated to indicate the address of the next instruction to be fetched. This allows the CPU to proceed to the next iteration of the machine cycle and continue executing instructions sequentially.

Proper management and organization of memory and registers are essential for optimal performance. CPUs employ various mechanisms, such as caches and memory management units, to facilitate efficient data storage and retrieval.

Overall, the storing stage of the machine cycle ensures that the executed results are safely stored and made available for further processing. By correctly updating memory and registers, the CPU maintains the program’s state and prepares for the next round of instruction execution.

Factors Affecting the Timing of CPU Work

The timing of CPU work, including the execution of instructions and the completion of machine cycles, is influenced by various factors. These factors can impact the overall performance and efficiency of the CPU. Let’s explore some of the key factors that affect the timing of CPU work.

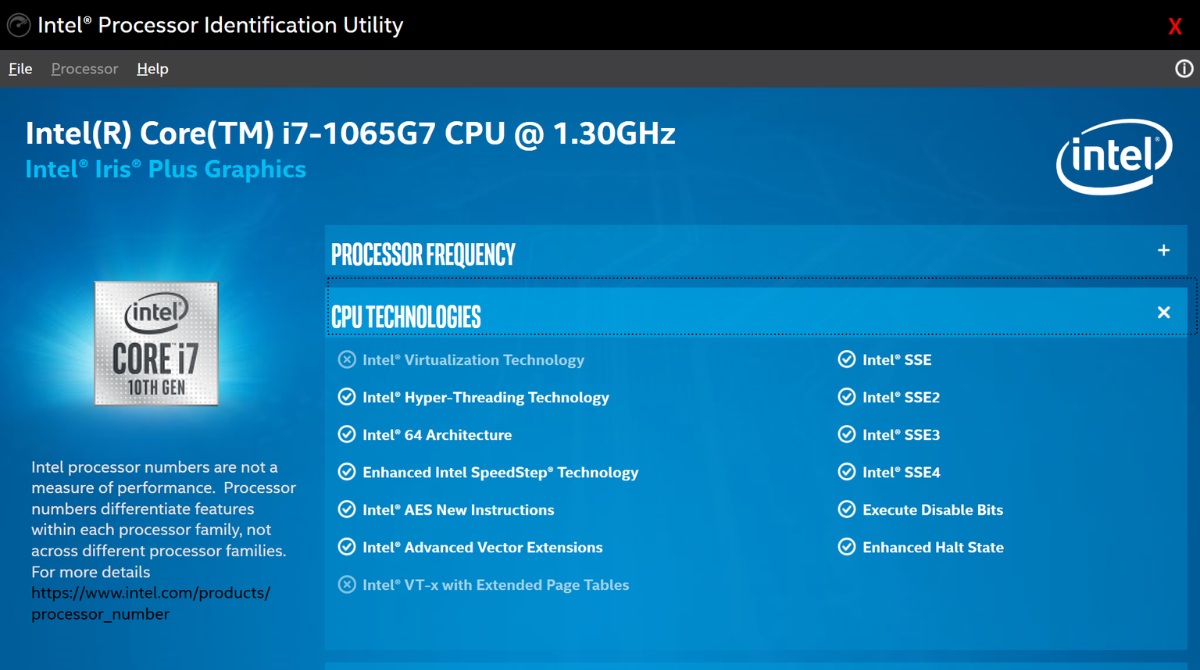

1. Clock Speed: The clock speed of the CPU, measured in Hertz (Hz), determines the number of instructions the CPU can execute per second. A higher clock speed allows for faster processing and shorter execution times. However, increasing the clock speed also leads to increased power consumption and heat generation, which can pose challenges in terms of cooling and energy efficiency.

2. Instruction Set Architecture (ISA): The ISA used by the CPU influences the complexity and efficiency of instruction execution. Different ISAs have different capabilities and instruction formats, which can impact the timing of CPU work. Advanced ISAs with specialized instructions and addressing modes can lead to faster execution and improved performance for specific tasks.

3. Cache Hierarchy: The CPU’s cache hierarchy, including levels of cache (L1, L2, L3), plays a crucial role in reducing memory access latency. Efficient cache utilization can significantly reduce the time it takes to fetch instructions and data from memory, leading to faster execution and improved performance.

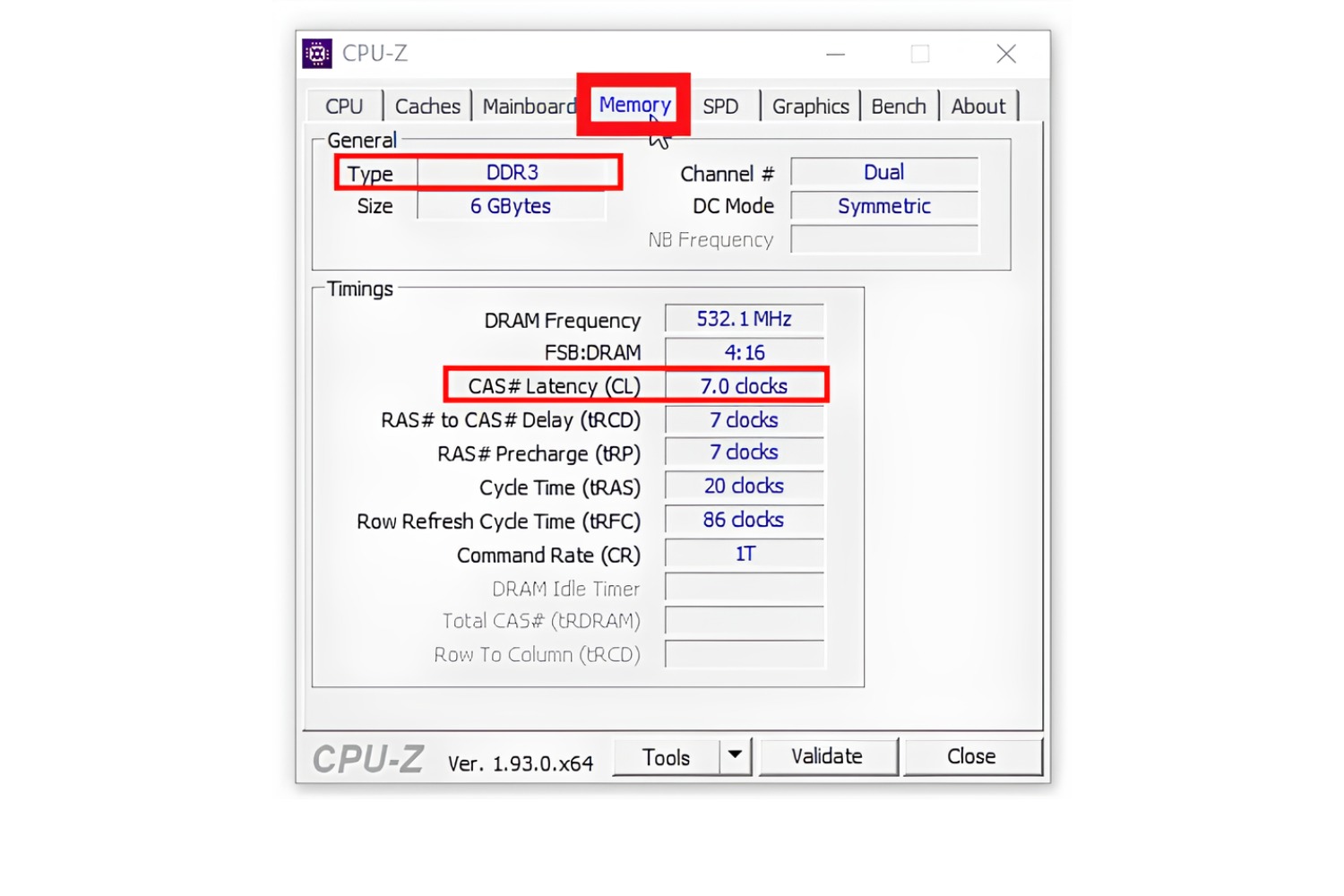

4. Memory Access: The speed and efficiency of accessing main memory or external devices can have a significant impact on CPU performance. Memory access latency, data transfer rates, and memory management techniques all affect the timing of CPU work. Advanced memory technologies like DDR4 or DDR5 can provide higher memory bandwidth and lower latencies, leading to faster data access.

5. Pipelining and Parallelism: Pipelining allows the CPU to overlap the execution of multiple instructions, reducing overall execution time. By breaking down instruction execution into smaller stages and overlapping them, pipelining improves efficiency and enables parallel execution of instructions. However, dependencies between instructions and pipeline stalls can impact the timing of CPU work.

6. Branch Prediction: Conditional branch instructions can disrupt the sequential execution of instructions and introduce delays. Branch prediction techniques aim to predict the outcome of conditional branches to speculatively execute subsequent instructions. Efficient branch prediction algorithms can minimize the impact of branching on CPU performance.

7. Data Dependencies: Dependencies between instructions that rely on the results of previous instructions can affect the timing of CPU work. These dependencies may require the CPU to stall or wait for the completion of a previous instruction before proceeding. Advanced techniques like out-of-order execution and register renaming help mitigate data dependencies and improve performance.

8. Instruction Cache Misses: When the CPU fetches an instruction that is not present in the instruction cache, a cache miss occurs. In such cases, the CPU needs to retrieve the instruction from main memory, which incurs a higher latency. Minimizing instruction cache misses through efficient cache management can improve the timing of CPU work.

It is important to note that the timing of CPU work can vary depending on the specific CPU architecture and implementation. Different CPUs have different designs and optimizations to balance factors such as power consumption, heat dissipation, and performance.

By considering and optimizing these factors, CPU designers and developers can work towards achieving faster execution times, improved overall performance, and enhanced efficiency.

Conclusion

Understanding the machine cycle of a CPU is essential to comprehend how instructions are processed and executed. It involves a series of stages, including fetching, decoding, executing, and storing, each contributing to the overall functionality and performance of the CPU.

During the machine cycle, the CPU retrieves instructions from memory, deciphers their meaning, carries out the specified operation, and stores the results. These stages are intricately connected, and efficient execution is crucial for optimal performance.

The timing of CPU work is influenced by various factors, including clock speed, instruction set architecture, cache hierarchy, memory access, pipelining, branch prediction, data dependencies, and instruction cache efficiency. These factors can impact the speed and efficiency of instruction execution, as well as the overall performance of the CPU.

By understanding and optimizing these factors, CPU designers and developers can improve the performance and efficiency of CPUs. Techniques such as pipelining, cache management, branch prediction, and memory optimizations can contribute to faster execution times and enhanced overall system performance.

The machine cycle and its associated factors play a vital role in the operation of modern CPUs. By continuously improving and optimizing these aspects, CPU technology continues to advance, delivering impressive computational power and efficiency.

In conclusion, the machine cycle of a CPU consists of fetching, decoding, executing, and storing instructions. The speed and efficiency of each stage, as well as the factors influencing CPU timing, determine the overall performance and efficiency of the CPU. Understanding and optimizing these aspects allows for the development of faster, more efficient CPUs that power the digital world we live in today.