Introduction

In the world of computing, speed and efficiency are crucial factors in determining the overall performance of a system. The CPU (Central Processing Unit) plays a pivotal role in this regard, as it is responsible for executing instructions and performing calculations. To optimize CPU performance, various techniques are employed, and one such technique is the use of cache.

Cache is a small, high-speed memory component present in the CPU. Its primary purpose is to store frequently accessed data and instructions, reducing the time taken to retrieve information from the main memory. By storing this data closer to the CPU, cache minimizes the latency that occurs when accessing larger and slower memory components.

Cache plays a vital role in enhancing overall system performance. It allows the CPU to quickly retrieve data and instructions, reducing the number of cycles spent waiting for information to be fetched from the main memory. This results in a significant improvement in computational speed, making cache an integral part of modern CPUs.

Cache operates on the principle of locality, which refers to the tendency of a program to access data and instructions that are close to each other in memory. There are two types of locality: temporal and spatial. Temporal locality suggests that recently accessed data is likely to be accessed again in the near future, while spatial locality indicates that data located nearby the recently accessed data is also likely to be accessed soon. Cache exploits both types of locality to maximize its effectiveness.

Understanding how cache works, the different cache levels, and techniques employed to manage cache plays a crucial role in optimizing CPU performance. In this article, we will delve deeper into cache and explore its various aspects, including its functionality in a CPU, cache hierarchy, cache coherence, and how cache hits and misses affect system performance.

What is Cache?

Cache is a small, high-speed memory component that is an integral part of modern computer systems, including CPUs. It serves as a buffer between the CPU and the main memory, storing frequently accessed data and instructions. The main purpose of cache is to minimize the time required to access data and instructions, thereby improving system performance.

Cache works on the principle of locality, which exploits the tendency of programs to access data and instructions that are close to each other in memory. This principle consists of two types: temporal locality and spatial locality. Temporal locality suggests that recently accessed data is likely to be accessed again in the near future. Spatial locality indicates that data located nearby the recently accessed data is also likely to be accessed soon. Cache takes advantage of these localities by storing recently accessed and neighboring data in its memory.

Cache operates at a much faster speed compared to the main memory. While the main memory is slower, it offers a larger capacity to store data and instructions. When the CPU needs to access data, it first checks the cache. If the required data is present in the cache, it is known as a cache hit. In this case, the CPU can access the data quickly, without having to go to the main memory. However, if the required data is not present in the cache, it is known as a cache miss, and the CPU has to fetch the data from the main memory, which takes longer and introduces a delay in the execution of instructions.

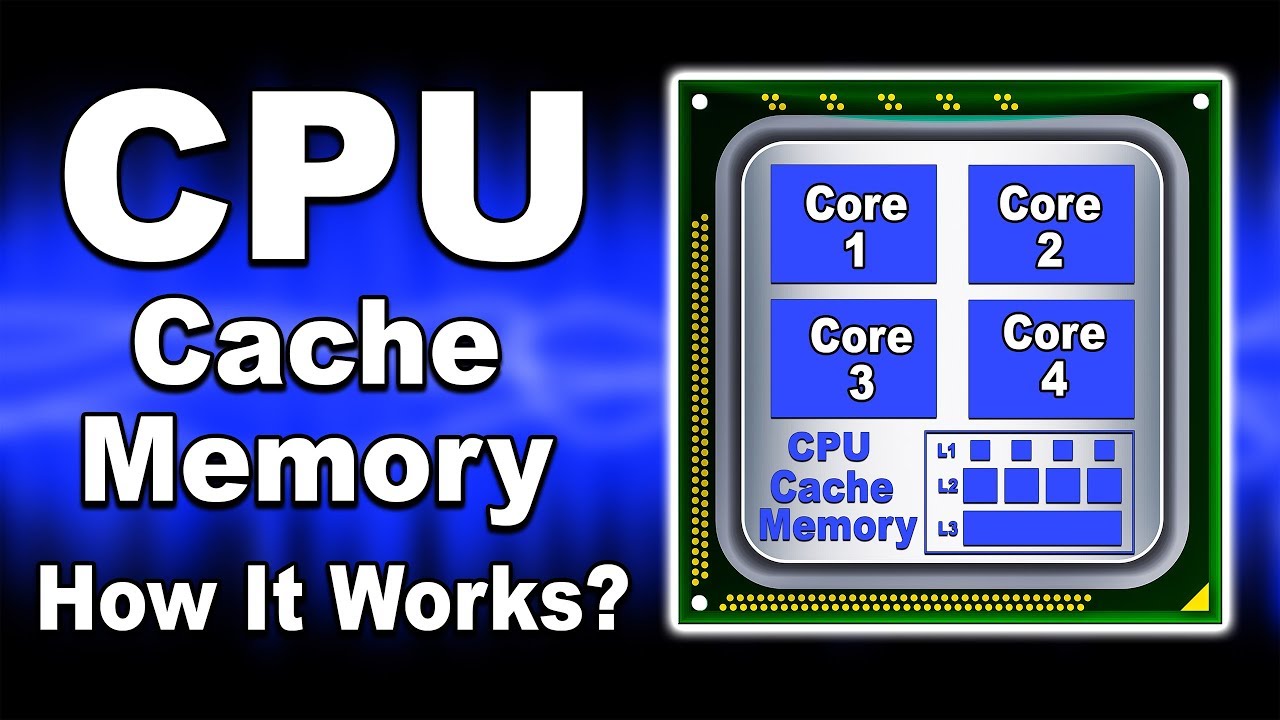

Cache is organized into different levels, known as cache levels or cache hierarchy. The highest level of cache, called L1 cache, is the closest to the CPU and has the smallest capacity but the fastest access time. L1 cache is divided into separate instruction and data caches to expedite the execution of instructions. As we move further from the CPU, the cache levels increase (L2, L3, etc.), offering larger capacities but at the cost of slightly slower access times.

In summary, cache is a critical component in modern computer systems that allows for faster access to frequently accessed data and instructions. By leveraging the principles of locality, cache improves the efficiency and speed of CPU operations, resulting in enhanced overall system performance.

Why is Cache Important?

Cache plays a crucial role in the overall performance of a computer system, particularly the CPU. Here are some key reasons why cache is important:

- Improved Speed: One of the primary benefits of cache is the significant improvement in system speed. By storing frequently accessed data and instructions closer to the CPU, cache reduces the amount of time spent waiting for data to be retrieved from the main memory. This leads to faster execution of instructions and overall faster processing times.

- Reduced Memory Latency: Cache acts as a buffer between the CPU and the main memory. Since cache operates at a much higher speed than the main memory, it reduces the memory latency, which is the time required to access data from the main memory. By minimizing memory latency, cache enhances the overall efficiency of the system.

- Optimized CPU Utilization: With cache, the CPU can access frequently used data and instructions without having to rely heavily on the relatively slower main memory. This means that the CPU can spend more time performing calculations and executing instructions, thereby optimizing its utilization and boosting overall system performance.

- Enhanced Power Efficiency: By minimizing the need to access the main memory, cache helps conserve power. Accessing the main memory requires more energy compared to accessing cache due to the inherent latency difference. Thus, cache reduces power consumption, making the system more power efficient.

- Improved User Experience: Cache significantly improves the user experience by enabling faster load times for applications, quicker response times, and seamless multitasking capabilities. With cache, data and instructions can be retrieved almost instantaneously, leading to a smoother and more responsive computing experience.

In today’s computing landscape, where speed and efficiency are highly valued, cache has become an indispensable component. It plays a vital role in ensuring that CPUs perform optimally and deliver the required computational power. Cache offers a balance between the high-speed access of data and the large capacity of the main memory, resulting in improved system performance and a more responsive user experience.

Types of Cache

Cache in computer systems can be categorized into different types based on their purpose and location. Let’s explore some of the common types of cache:

- Level 1 (L1) Cache: L1 cache is the first level of cache and is directly integrated into the CPU. It consists of separate instruction and data caches. The instruction cache stores frequently used instructions, while the data cache stores frequently accessed data. Being closest to the CPU, L1 cache has the smallest capacity but the fastest access time.

- Level 2 (L2) Cache: L2 cache is the second level of cache and is located between the L1 cache and the main memory. It has a larger capacity compared to L1 cache but slightly slower access times. L2 cache helps bridge the gap between the high-speed L1 cache and the larger but slower main memory.

- Level 3 (L3) Cache: L3 cache is a higher-level cache that provides additional capacity and acts as a buffer between the lower-level caches and the main memory. It is typically shared among multiple CPU cores in a multi-core processor. L3 cache serves to further reduce the latency between the CPU cores and the main memory.

- Unified Cache: Unified cache is a type of cache that combines both instruction and data caches into a single cache. It eliminates the need for separate instruction and data caches, simplifying cache management and reducing the overall complexity of the CPU architecture.

- Write-through Cache: In a write-through cache, any write operation to the cache is immediately propagated to the main memory. This ensures that the data in the cache is always synchronized with the main memory, but it may introduce additional latency as every write operation requires accessing the main memory.

- Write-back Cache: In a write-back cache, write operations are initially performed only in the cache. The modification is then later copied to the main memory when the cache line is evicted or when a specific condition is met. Write-back cache can improve performance by reducing the frequency of memory writes, but there is a risk of data loss if the system encounters a sudden power loss or crash.

Each type of cache serves a specific purpose in optimizing CPU performance and minimizing the latency between the CPU and the main memory. The choice of cache type depends on factors such as the CPU architecture, intended use case, and performance requirements of the system.

How Does Cache Work in a CPU?

Cache is an essential component of a CPU that helps improve performance by reducing the latency in retrieving data from the main memory. Let’s explore how cache works in a CPU:

When the CPU needs to access data or instructions, it first checks the cache for their presence. This is known as a cache lookup or cache access. Cache operates on the principle of locality, which exploits the tendency of programs to access data and instructions that are close to each other in memory. It utilizes two types of locality: temporal locality and spatial locality.

Temporal locality refers to the idea that recently accessed data is likely to be accessed again in the near future. When the CPU retrieves data from the main memory, it stores a copy of that data in the cache. If the CPU needs to access the same data again, it can retrieve it directly from the cache, resulting in a cache hit. This avoids the need to go through the slower process of accessing the main memory, thus reducing the latency and improving performance.

Spatial locality suggests that data located nearby the recently accessed data is also likely to be accessed soon. When the CPU retrieves a piece of data from the main memory, it also fetches a certain amount of neighboring data and stores it in the cache. This anticipates the CPU’s future data needs and reduces the number of cache misses, further minimizing the latency in accessing data.

Cache is organized into different levels, with each level having a specific capacity and access time. The highest-level cache, L1 cache, is the closest to the CPU and has the fastest access time. As we move down the hierarchy, the cache levels offer more capacity but slightly slower access times. This hierarchy allows for a balance between speed and capacity.

When the CPU performs a cache lookup, it first checks the L1 cache. If the required data is present in the L1 cache, it is known as an L1 cache hit. The CPU can quickly retrieve the data from the L1 cache and proceed with the execution of instructions. However, if the required data is not found in the L1 cache, it is considered an L1 cache miss. In this case, the CPU moves to the next level of cache, such as L2 or L3, and repeats the lookup process. If the data is found in any of these caches, it is considered a cache hit, and the data is retrieved. Otherwise, it is a cache miss, and the CPU has to fetch the data from the main memory, which introduces additional latency.

In summary, cache in a CPU works by storing frequently accessed data and instructions closer to the CPU, reducing the latency in retrieving information from the main memory. By leveraging the principles of temporal and spatial locality, cache minimizes cache misses and maximizes cache hits, resulting in improved system performance and faster execution of instructions.

Cache Hierarchy

Cache hierarchy refers to the organization of different cache levels in a computer system, typically found in CPUs. This hierarchy allows for a balance between speed and capacity, optimizing the overall performance of the system. Let’s explore the cache hierarchy in more detail:

The cache hierarchy consists of multiple levels of cache, with each level closer to the CPU offering faster access times but smaller capacities. The highest-level cache, known as Level 1 (L1) cache, is the fastest but has the smallest capacity. It is designed to store frequently accessed data and instructions to reduce latency and enhance performance. The L1 cache is divided into separate instruction and data caches, enabling independent retrieval and processing of instructions and data.

As we move further away from the CPU, we encounter the Level 2 (L2) cache. The L2 cache has a larger capacity but slightly slower access times compared to the L1 cache. It acts as a middle layer between the L1 cache and the main memory, serving as a buffer to bridge the performance gap. The L2 cache helps reduce the latency in accessing data from the main memory and improves overall system efficiency.

In some cases, there may be additional cache levels beyond L2, such as Level 3 (L3) cache. The L3 cache is often shared among multiple CPU cores in a multi-core processor, providing a larger capacity compared to the L2 cache. It further helps reduce the latency between the CPU cores and the main memory, enhancing the overall system performance in multi-threaded applications.

The cache hierarchy operates on the principle of data movement between different cache levels. When a CPU retrieves data or instructions, it first checks the smallest and fastest cache level, which is the L1 cache. If the required data is not found in the L1 cache, a cache miss occurs, and the CPU moves on to the next cache level (e.g., L2 or L3) to perform a cache lookup. The process continues until the data is found in one of the cache levels or a cache miss occurs at the last level, requiring the CPU to fetch the data from the main memory.

The cache hierarchy provides an effective compromise between the speed of accessing data and the capacity to store data. It allows for quick access to frequently accessed data and instructions by utilizing faster but smaller cache levels. At the same time, it utilizes larger but slower cache levels or the main memory to accommodate a larger amount of data that is less frequently accessed. This organization ensures that the CPU can efficiently retrieve and process data, optimizing the overall performance of the system.

Cache Levels

Cache levels refer to the different levels of cache within a computer system, typically found in the CPU. These cache levels are designed to provide varying capacities and access times, catering to the specific needs of the system. Let’s take a closer look at the different cache levels:

Level 1 (L1) Cache: L1 cache is the first level of cache and is the closest to the CPU. It is divided into separate instruction and data caches. The instruction cache (L1i cache) stores frequently used instructions, while the data cache (L1d cache) stores frequently accessed data. L1 cache has the smallest capacity among the cache levels but offers the fastest access times. Its proximity to the CPU ensures quick retrieval of data and instructions, reducing latency and improving performance.

Level 2 (L2) Cache: L2 cache is the second level of cache and is located between the L1 cache and the main memory. It has a larger capacity compared to the L1 cache but slower access times. The L2 cache acts as a buffer, bridging the performance gap between the faster L1 cache and the larger but slower main memory. It helps reduce the latency in accessing data from the main memory, contributing to improved system efficiency.

Level 3 (L3) Cache: L3 cache is a higher-level cache that is often shared among multiple CPU cores in a multi-core processor. It provides additional capacity compared to the L2 cache and helps further reduce the latency between the CPU cores and the main memory. The L3 cache is particularly effective in improving the overall performance of multi-threaded applications, where multiple CPU cores are simultaneously accessing data.

The cache levels operate in a hierarchical manner, with each level storing data and instructions that are frequently accessed or are anticipated to be accessed soon. When the CPU needs to access data, it first checks the smallest and fastest cache level (L1 cache). If the data is present in the L1 cache, it is considered a cache hit, and the CPU can quickly retrieve the data. However, if the data is not found, a cache miss occurs, and the CPU moves on to the next cache level (e.g., L2 or L3) to perform a cache lookup. This process continues until the data is found in one of the cache levels or a cache miss occurs at the last level, necessitating a fetch from the main memory.

The cache levels work together to optimize the retrieval and processing of data, balancing the need for speed and capacity. Each cache level contributes to reducing the latency in accessing data, ultimately improving the overall performance of the system. The specific configuration and number of cache levels within a CPU may vary depending on the architecture and design choices made by the processor manufacturer.

Cache Coherence

Cache coherence refers to the consistency of data across multiple caches in a computer system. In systems with multiple processors or CPU cores that have their own cache, maintaining cache coherence is essential to ensure data integrity and the proper execution of programs. Let’s delve deeper into the concept of cache coherence:

When multiple processors or CPU cores share a common memory space, each processor or core may have its own cache to store frequently accessed data. As a result, it is possible for different caches to have a copy of the same data. However, this presents a challenge—what happens when one processor or core modifies a piece of data in its cache? The other processors or cores that also have a copy of that data in their caches need to be aware of this modification to ensure data consistency.

Cache coherence protocols are employed to manage cache coherence. These protocols ensure that all caches within the system have a consistent view of the shared data. There are several cache coherence protocols, and their complexity and implementation may vary depending on the system architecture. However, the primary goal is to allow different caches to communicate and coordinate their actions to maintain data consistency.

One common cache coherence protocol is the MESI protocol, which stands for Modified, Exclusive, Shared, and Invalid. In this protocol, each cache line has a state that indicates its current status. The modified state indicates that the cache line has been modified and is not consistent with the main memory. The exclusive state implies that the cache line is clean and not shared with other caches. The shared state represents that the cache line is consistent with the main memory and can be shared with other caches. The invalid state indicates that the cache line is not valid and needs to be refreshed from the main memory.

Cache coherence protocols implement mechanisms such as invalidation and updates to ensure data consistency. When one core modifies a cache line, it communicates with the other cores using a bus or network to invalidate their copies of the same cache line. This forces the other cores to fetch the latest copy from the main memory when they need to access that data. Alternatively, in some protocols, the modified cache line is updated in the main memory, making it visible to other cores when accessed again.

Maintaining cache coherence is crucial for the proper functioning of multi-core processors and systems with multiple processors. It ensures that all cores or processors work with consistent and up-to-date data, preventing data corruption and erroneous program execution. Cache coherence protocols form a key part of the overall system architecture and help maintain data integrity in complex computing environments.

Managing Cache

Managing cache effectively is crucial for optimizing system performance and ensuring data integrity in a computer system. To achieve efficient cache management, several techniques and mechanisms are employed. Let’s explore some common practices for managing cache:

Cache Inclusion and Exclusion: Cache inclusion refers to the practice of including data in a higher-level cache if it exists in a lower-level cache. This ensures that data is available at each cache level, reducing cache misses and improving the overall performance. Cache exclusion, on the other hand, entails removing unused or less frequently accessed data from the cache to make room for more relevant data. This helps prevent cache thrashing and optimizes cache utilization.

Cache Replacement Policies: Cache replacement policies dictate how the cache chooses which data to evict when new data needs to be inserted and the cache is full. Common replacement policies include Least Recently Used (LRU), where the least recently accessed data is evicted, and Random, where data is evicted randomly. The choice of replacement policy depends on the system’s specific requirements, workload characteristics, and trade-offs between performance and complexity.

Cache Prefetching: Cache prefetching is a technique that anticipates the CPU’s future memory access patterns and proactively brings data into the cache before it is actually needed. By predicting the data that is likely to be accessed next, cache prefetching can help minimize cache misses and reduce the latency in accessing data.

Cache Write Policies: Cache write policies determine how and when data modifications are written back to the main memory. Write-through policies write modifications to both the cache and the main memory simultaneously, ensuring data consistency but potentially introducing additional latency. Write-back policies, on the other hand, write modifications to the cache only and defer updating the main memory until it becomes necessary. This can improve performance but carries the risk of data inconsistency in case of system failures.

Cache Coherency Mechanisms: As discussed in the previous section, cache coherence protocols ensure that multiple caches have a consistent view of shared data. These protocols implement mechanisms such as invalidation and updates to maintain data integrity and coherency across cache levels.

Effective cache management requires a delicate balance between different techniques and mechanisms based on the specific system requirements and workload characteristics. Careful consideration should be given to cache size, replacement policies, prefetching strategies, and write policies to optimize cache performance and utilization. Additionally, cache management techniques should be tailored to the specific architecture and design choices of the system to achieve the desired level of performance and efficiency.

Cache Misses and Cache Hits

Cache misses and cache hits are crucial concepts that determine the efficiency and performance of a cache system within a computer. Let’s explore these terms and their impact on system operations:

A cache hit occurs when the processor or CPU successfully finds the required data or instruction in the cache. In this case, the CPU can quickly retrieve the data without accessing the slower main memory, resulting in reduced latency and faster execution. Cache hits are desirable as they improve system performance by providing timely access to frequently used data.

On the other hand, a cache miss occurs when the CPU fails to find the needed data or instruction in the cache. In such cases, the CPU has to access the main memory to fetch the required data. This introduces additional latency and can significantly impact performance, as accessing the main memory is slower compared to accessing the cache. Cache misses are generally undesirable because they delay the CPU’s execution and may result in performance bottlenecks.

Cache misses can be further classified into two types: cold misses and capacity misses. A cold miss occurs when the cache is initially empty, or when the CPU tries to access data that has not been previously loaded into the cache. These misses are common during system startup or when a new program begins execution. Capacity misses, on the other hand, occur when the cache is full and there is not enough space to store all the necessary data. This can happen when a program has a larger working set than what the cache can accommodate.

Reducing cache misses and maximizing cache hits is crucial for improving system performance. Strategies to minimize cache misses include cache prefetching, where the CPU predicts future memory access patterns and proactively brings data into the cache. Optimizing cache replacement policies, such as using the least recently used (LRU) algorithm, can also help reduce cache misses.

Cache hits and misses directly impact the overall efficiency and speed of a computer system. A high cache hit rate indicates that the cache is effectively storing and retrieving frequently used data, resulting in improved performance. Conversely, a high cache miss rate suggests that the cache is not adequately meeting the CPU’s data retrieval needs, leading to performance degradation.

Analyzing and optimizing cache hit and miss rates is an important aspect of system performance monitoring and tuning. By carefully examining these metrics, system designers and developers can identify bottlenecks, improve cache management techniques, and fine-tune program execution to enhance cache utilization and overall system efficiency.

Conclusion

Cache plays a critical role in improving the speed and efficiency of a computer system, especially in the CPU. It stores frequently accessed data and instructions, reducing the latency in retrieving information from the main memory. By leveraging the principles of locality, cache minimizes cache misses and maximizes cache hits, resulting in enhanced system performance.

We explored various aspects of cache, including its functionality in a CPU, cache hierarchy, cache coherence, and the significance of managing cache effectively. Cache levels, such as L1, L2, and L3, provide a balance between capacity and access time, optimizing the performance of multi-level cache systems. Cache coherence ensures data consistency across multiple caches, while managing cache involves techniques such as cache inclusion and exclusion, cache replacement policies, prefetching, write policies, and cache coherency mechanisms.

Cache hits and cache misses directly impact system performance, with cache hits resulting in faster execution of instructions and cache misses introducing latencies due to accessing the main memory. Fine-tuning cache management techniques and monitoring cache hit and miss rates is crucial for optimizing system performance and improving overall efficiency.

In conclusion, cache is a vital component of modern computer systems, allowing for quicker access to frequently used data and instructions. By minimizing the latency of memory access and optimizing system performance, cache significantly enhances the user experience and enables faster execution of computational tasks. The continued development and refinement of cache technologies contribute to the advancement of computing capabilities and facilitate the efficient use of resources in a wide range of applications.